Edition 1.0 2016-11

# INTERNATIONAL IEEE Std 2401™ STANDARD

Format for LSI-Package-Board interoperable design

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ICS 31.180; 31.200; 35.060

ISBN 978-2-8322-3686-4

Warning! Make sure that you obtained this publication from an authorized distributor.

## Contents

| <ol> <li>Overview</li></ol>                                                                                                                                                           | 1<br>1<br>1<br>        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 2. Normative references                                                                                                                                                               |                        |

| <ol> <li>Definitions, acronyms, and abbreviations</li></ol>                                                                                                                           |                        |

| <ul> <li>4. Concept of the LPB Format</li></ul>                                                                                                                                       | 8<br>8<br>9<br>9<br>10 |

| 5. Language basics                                                                                                                                                                    | 16                     |

| <ul> <li>6. Common elements in M-Format, C-Format, and R-Format</li> <li>6.1 General</li> <li>6.2 The <header> element</header></li> <li>6.3 The <global> element</global></li> </ul> |                        |

| <ul> <li>7. M-Format</li> <li>7.1 M-Format file structure</li> <li>7.2 The <include> element</include></li> <li>7.3 The <class> element</class></li> </ul>                            |                        |

| <ul> <li>8. C-Format</li></ul>                                                                                                                                                        |                        |

| <ul> <li>9. R-Format</li></ul>                                                                                                                                                        |                        |

| <ul> <li>10. N-Format</li> <li>10.1 Purpose of the N-Format file</li> <li>10.2 How to identify the power/ground network</li> <li>10.3 Example</li> </ul>                              |                        |

| <ul><li>11. G-Format</li><li>11.1 Language basics of G-Format</li><li>11.2 Structure</li></ul>                                                                                        |                        |

| 11.3 Header section                                             |     |

|-----------------------------------------------------------------|-----|

| 11.4 Material section                                           |     |

| 11.5 Layer section                                              |     |

| 11.6 Shape section                                              |     |

| 11.7 Board geometry section                                     |     |

| 11.8 Padstack section                                           |     |

| 11.9 Part section                                               |     |

| 11.10 Component section                                         |     |

| 11.11 Net attribute section                                     |     |

| 11.12 Netlist section                                           |     |

| 11.13 Via section                                               |     |

| 11.14 Bondwire section                                          |     |

| 11.15 Route section                                             |     |

|                                                                 |     |

| Annex A (informative) Bibliography                              |     |

|                                                                 |     |

| Annex B (informative) Examples of utilization                   |     |

| B.1 Understanding the function of the LPB Format                |     |

| B.2 Test bench                                                  |     |

| B.3 Design flow example                                         |     |

| B.4 Growth of the sample files in the LPB Format                |     |

| B.5 Simulations using the sample files in the LPB Format        |     |

|                                                                 |     |

| Annex C (informative) XML Encryption                            |     |

| ······································                          |     |

| Annex D (informative) MD5 checksum                              |     |

|                                                                 |     |

| Annex E (informative) Chip-Package Interface Protocol           | 188 |

| E.1 General                                                     |     |

| E.2 Comparison of C-Format with Chip-Package Interface Protocol |     |

|                                                                 |     |

| Annex F (informative) IEEE list of participants                 | 10/ |

| Annex I (informative) IEEE list of participants                 | 194 |

### FORMAT FOR LSI-PACKAGE-BOARD INTEROPERABLE DESIGN

### FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and nongovernmental organizations liaising with the IEC also participate in this preparation.

IEEE Standards documents are developed within IEEE Societies and Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board. IEEE develops its standards through a consensus development process, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of IEEE and serve without compensation. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards. Use of IEEE Standards documents is wholly voluntary. IEEE documents are made available for use subject to important notices and legal disclaimers (see http://standards.ieee.org/IPR/disclaimers.html for more information).

IEC collaborates closely with IEEE in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees. The formal decisions of IEEE on technical matters, once consensus within IEEE Societies and Standards Coordinating Committees has been reached, is determined by a balanced ballot of materially interested parties who indicate interest in reviewing the proposed standard. Final approval of the IEEE standards document is given by the IEEE Standards Association (IEEE-SA) Standards Board.

- 3) IEC/IEEE Publications have the form of recommendations for international use and are accepted by IEC National Committees/IEEE Societies in that sense. While all reasonable efforts are made to ensure that the technical content of IEC/IEEE Publications is accurate, IEC or IEEE cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications (including IEC/IEEE Publications) transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC/IEEE Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC and IEEE do not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC and IEEE are not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or IEEE or their directors, employees, servants or agents including individual experts and members of technical committees and IEC National Committees, or volunteers of IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board, for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC/IEEE Publication or any other IEC or IEEE Publications.

- 8) Attention is drawn to the normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that implementation of this IEC/IEEE Publication may require use of material covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. IEC or IEEE shall not be held responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patent Claims or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility.

International Standard IEC 63055/IEEE Std 2401 has been processed through IEC technical committee 91: Electronics assembly technology, under the IEC/IEEE Dual Logo Agreement.

The text of this standard is based on the following documents:

| IEEE Std    | FDIS         | Report on voting |

|-------------|--------------|------------------|

| 2401 (2015) | 91/1362/FDIS | 91/1373/RVD      |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

The IEC Technical Committee and IEEE Technical Committee have decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

IEC 63055:2016 IEEE Std 2401-2015

# IEEE Standard Format for LSI-Package-Board Interoperable Design

Sponsor

Design Automation Standards Committee of the IEEE Computer Society

Approved 3 September 2015

**IEEE-SA Standards Board**

Published by IEC under license from IEEE.  $\ensuremath{\textcircled{o}}$  2015 IEEE. All rights reserved.

### Copyrights and Permissions

The following figures are reprinted with permission from JEITA<sup>1</sup>

Figure i, Figure 1, Figure 3, Figure 16, Figure 17, Figure 18, Figure 19, Figure 20, Figure 21, Figure 22, Figure 23, Figure 24, Figure 25, Figure 26, Figure 27, Figure 28, Figure 29, Figure 30, Figure 31, Figure 32, Figure 33, Figure 34, Figure 35, Figure 36, Figure 37, Figure 38, Figure 39, Figure 40, Figure 41, Figure 42, Figure 43, Figure 44, Figure 45, Figure 46, Figure 47, Figure 48, Figure 49, Figure 50, Figure 51, Figure 60, Figure 61, Figure 62, Figure 63, Figure B.1, Figure B.3, Figure B.5, Figure B.6, Figure B.7, Figure B.8, Figure B.10, Figure B.11, Figure B.12, Figure B.13, Figure B.14, Figure B.15, Figure B.16, Figure B.17, Figure B.18, Figure B.19, Figure B.20, Figure B.21, Figure B.22, Figure B.23, Figure B.24, Figure B.25, Figure B.26, Figure B.27, Figure B.28, Figure B.29

**Abstract:** A method is provided for specifying a common interoperable format for electronic systems design. The format provides a common way to specify information/data about the project management, netlists, components, design rules, and geometries used in Large-Scale Integrated Circuit-Package-Board designs. The method provides the ability to make electronic systems a key consideration early in the design process; design tools can use it to exchange information/data seamlessly.

**Keywords:** common interoperable format, components, design analysis, design rules, geometries, IEEE 2401<sup>™</sup>, large-scale integrated circuits, netlists, packages for LSI circuits, printed circuit board, project management, Verilog-HDL

Published by IEC under license from IEEE.  $\ensuremath{\texttt{©}}$  2015 IEEE. All rights reserved.

## **IEEE Introduction**

This introduction is not part of IEEE Std 2401<sup>™</sup>-2015, IEEE Standard Format for LSI-Package-Board Interoperable Design.

To deal with the increasing difficulty of design and the cost competitiveness of the global market, and to shorten the development term, innovative design methodologies should be implemented. It has been difficult to achieve the optimization of an entire set of large-scale integrated (LSI) circuits, packages, and board (LPB) using individual design processes for each LPB part.

One possibility for optimization is to have a certain section design the whole LPB; however, gathering knowledge and integrating the design environment of each LPB part is difficult. Dedicated professional technicians of individual LPB parts, who have the best knowledge and performance of their own part's design tools, intend to create design optimization by having proper interoperable information exchanges among all LPB parties. In order to achieve a design that optimizes the balance between cost and performance, information about and the results of design should be well shared among cooperating LPB design sections.

The Japan Electronics and Information Technology Industries Association (JEITA) LPB Interoperable Design Process Working Group (LPB-WG) was established to identify the solution. The LPB-WG intends to make a standard for an exchange format to make it easy to exchange information between each of the LPB design departments, so that optimal design will be carried out quickly.

The LPB interoperable design process has the following issues:

- Netlist not unified on each LPB

- Complexity of the representation of the relationship as a whole arrangement of the LPB

- Differences in how to give the design constraints, lack of design information, and many discrepancies in design rules.

- Databases not unified in each LPB, or among different vendors

- No unified terms

Various problems caused by these issues include the following:

- A large effort is required for conversion of formats.

- The occurrence of conversion errors and connection errors is difficult to detect because there is a lack of the information needed to do so.

- It takes a long time to gather information, resulting in a long period of design and analysis.

- It is difficult to make optimal design changes because the entire verification process is difficult.

- EDA tool cost increase because of additional development required to support multiple formats.

- It is time-consuming for designers to communicate their intentions in a way that others understand.

Based on this analysis, the LPB-WG has established an interface format that can address these issues.

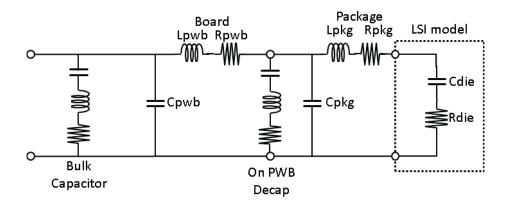

As the one of the case studies of the LPB interoperable design process, the power distribution network (PDN) should be designed with information about the other LPB parts to reduce the noise (see Figure i).

Reprinted with permission from JEITA.

#### Figure i—Power distribution network

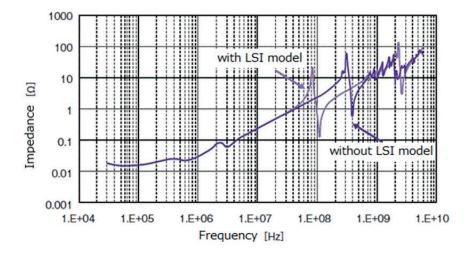

Resonance is caused by a capacitance and inductance present in the various parts in the LPB PDN. Impedance at the resonant frequency will be extremely large. If each part of the overall LPB design is not accurately simulated in the PDN model, the power supply circuit cannot be correctly designed (see Figure ii).

#### Figure ii—Example of PDN impedance

In order to run properly, this simulation should align a variety of information, such as the circuit model of power distribution network (PDN) of LSI, shape information about the package and board, electrical parameters of materials, and models of the components. It is difficult to make an efficient design when the specification or format of the design information is different in each part of the LPB, and the necessary parameters are not shared. When the format of the interface methods and models of the simulation are not consistent, the setup time and the cost of design/verification are enormous, which has become a barrier to cooperation in LPB design. The LPB-WG was established in JEITA to explore ways to create a mutual LPB interface to enable a more efficient co-design environment.

# Format for LSI-Package-Board Interoperable Design

IMPORTANT NOTICE: IEEE Standards documents are not intended to ensure safety, security, health, or environmental protection, or ensure against interference with or from other devices or networks. Implementers of IEEE Standards documents are responsible for determining and complying with all appropriate safety, security, environmental, health, and interference protection practices and all applicable laws and regulations.

This IEEE document is made available for use subject to important notices and legal disclaimers. These notices and disclaimers appear in all publications containing this document and may be found under the heading "Important Notice" or "Important Notices and Disclaimers Concerning IEEE Documents." They can also be obtained on request from IEEE or viewed at http://standards.ieee.org/IPR/disclaimers.html.

### 1. Overview

### 1.1 Scope

This standard defines a common interoperable format that will be used for the design of a) large-scale integration (LSI), b) packages for such LSI, and c) printed circuit boards on which the packaged LSI are interconnected. Collectively, such designs are referred to as" LSI-Package-Board" (LPB) designs. The format provides a common way to specify information/data about the project management, netlists, components, design rules, and geometries used in LPB designs.

### 1.2 Purpose

The general purpose of this standard is to develop a common format that LPB design tools can use to exchange information/data seamlessly, as opposed to having to work with multiple different input and output formats.

### **1.3 Key characteristics of the LSI-Package-Board Format**

LPB format will facilitate the exchange of design information. This functionality provides the ability to plan the entire design at an early stage. In effect, post-design analysis will be possible throughout the entire

LPB design process. Analysis of each part of the design can be examined in relation to all other parts of the design, to determine the optimal point to give feedback for appropriate design changes throughout the LPB. This will promote the overall optimization of the design process.

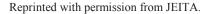

The LPB Format is constructed out of the following five formats (see Figure 1):

- a) Project Manage (M-Format)

- b) Netlist (N-Format)

- c) Component (C-Format)

- d) Design Rule (R-Format)

- e) Geometry (G-Format)

Reprinted with permission from JEITA.

### Figure 1—LPB Format

Design time can be shortened by using the LPB Format. Traditionally, design starts immediately after separate planning for each individual component of the LPB. Therefore, information exchange among the separate design processes is limited. Trying to adjust the detailed design of one component to the detailed design of another component makes the entire design period take longer. Optimization also tends to be a separate process for each component of the LPB. By using the LPB Format for distributing information, each LPB technician will be able to have the same understanding of the challenges at an early stage. As a result, adjustments at the conceptual design stage can be made, before detailed designs are developed. By making clear the overall LPB product specifications, the design target can be decided, and so the duration of individual designs can be shortened. Use of the LPB Format also helps to reduce the number of design iterations, because the design quality is enhanced. The designers can collect all information for simulation

using the LPB formats, thereby reducing production time. The LPB Format can enable the entire analysis easily, so that sufficient verification can be done and the quality of the products can be improved. As a result, the period of adjustment in the set can be shortened and the time to market can be accelerated. With the LPB Format, the design method for one product can be applied to the design environment for next product in development.

### 1.4 Contents of this standard

The organization of the remainder of this standard is as follows:

- Clause 2 provides references to other applicable standards that are presumed or required for this standard.

- Clause 3 defines terms and acronyms used throughout the different specifications contained in this standard.

- Clause 4 describes the concepts of the LPB Format.

- Clause 5 describes the language basics for the LPB Format and its commands.

- Clause 6 describes common elements in the M-Format, C-Format, and R-Format.

- Clause 7 describes the M-Format.

- Clause 8 describes the C-Format.

- Clause 9 describes the R-Format.

- Clause 10 describes the N-Format.

- Clause 11 describes the G-Format.

### 2. Normative references

The following referenced documents are indispensable for the application of this document (i.e., they must be understood and used, so each referenced document is cited in text and its relationship to this document is explained). For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments or corrigenda) applies.

IEEE Std 1364<sup>TM</sup>, IEEE Standard for Verilog Hardware Description Language.<sup>1,2</sup>

<sup>1</sup> IEEE publications are available from The Institute of Electrical and Electronics Engineers (<u>http://standards.ieee.org/</u>).

<sup>2</sup> The IEEE standards or products referred to in this clause are trademarks of The Institute of Electrical and Electronics Engineers, Inc.